Detector Readout Systems

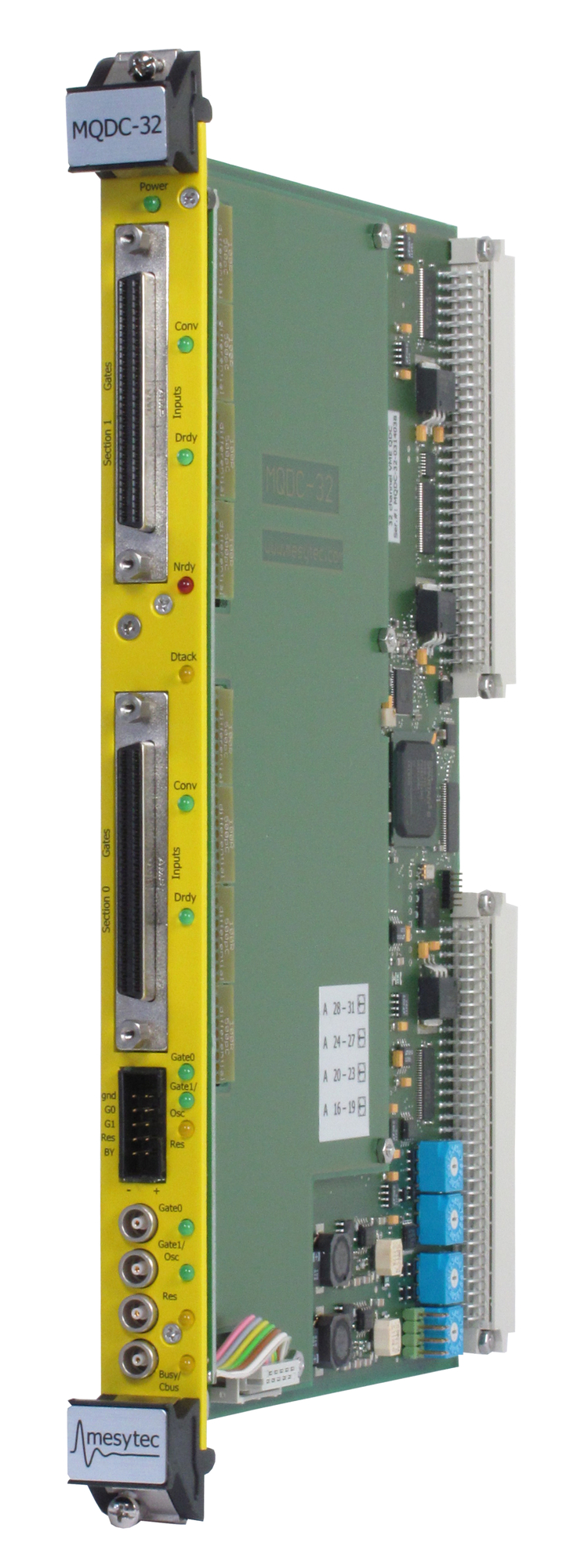

mesytec MQDC-32 is a fast 32 channel charge integrating ADC with individual gates. It provides a 12 bit (4 k) resolution with low differential non linearity due to sliding scale method. The total dead time is 250 ns for an event with all 32 channels responding.

It supports zero suppression with individual thresholds. Special features: Built-in pulse shape discrimination with 32 gate generators. Delayed gating with experiment trigger possible.

It supports zero suppression with individual thresholds. Special features: Built-in pulse shape discrimination with 32 gate generators. Delayed gating with experiment trigger possible.

Features

- High quality 12 bit (4 k) conversion with sliding scale ADC

(DNL <2 %) - 250 ns conversion and clear time for 32 channels

- Delayed gating with experiment trigger

- 64 k (32 bit-) words multi event buffer

(1 word corresponds to 1 converted channel

-> 2 k to 21 k events total) - Multiplicity filter, selects events on specified mult.-range

- Configurable: Individual gates or common gate

- Zero suppression with individual thresholds

- Supports different types of time stamping

- Independent bank operation

- Polarity is jumper selectable

(for processing dynode or anode signals) - Sensitivity and input resistance can be configured by special gain jumpers (50 pC to some nC. Default 500 pC)

- Signal input unipolar or differential (jumper configurable)

Differential inputs allow easy delay by twisted pair cables - AC coupled and baseline restored inputs.

Optional DC-coupled via register setting - Easy to use pulse shape analysis capability by 32 individual gate generators (4.5 ns to 300 ns)

- Gate and differential control inputs ECL, LVDS and PECL

can be terminated via register setting - mesytec control bus to control external mesytec modules

- Address modes: A24 / A32

- Data transfer modes: D16 (registers),

D32, BLT32, MBLT64, CBLT, CMBLT64 - Multicast for event reset and time stamping start

- Live insertion (can be inserted in a running crate)

- low power consumption (12 W)

© 2025 mesytec GmbH & Co. KG